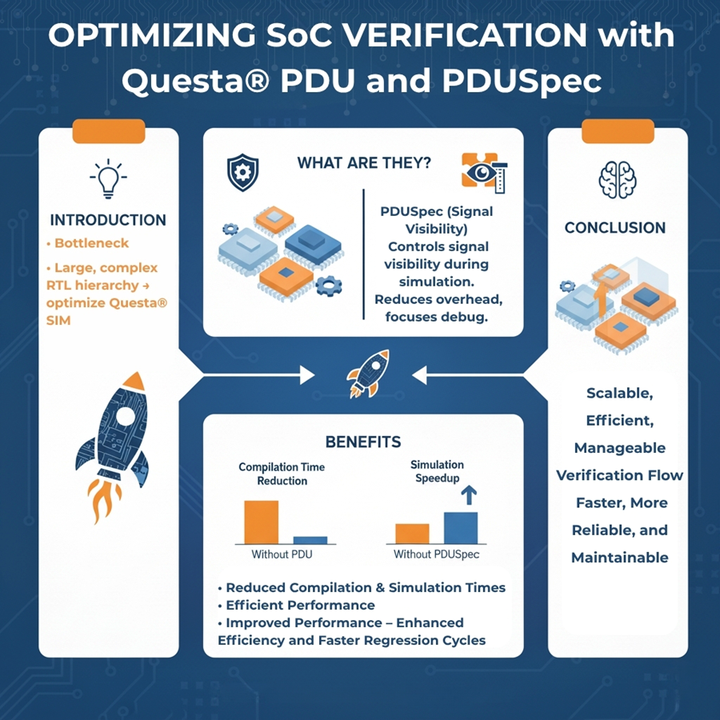

📘 Introduction

In a recent SoC verification project, I worked on optimizing the testbench setup in Questa® SIM to handle a large and complex RTL hierarchy efficiently. For large-scale designs, compilation and simulation times can be a major bottleneck, especially when multiple subsystems and hierarchical modules are involved. To address this, I leveraged PDU (Pre-Optimized Design Unit) and PDUSpec effectively.

🧩 What is PDU (Pre-Optimized Design Unit)?

PDU allows portions of the design to be compiled and optimized independently. Instead of re-optimizing the entire design every time, stable subsystems are pre-compiled into PDUs. This drastically reduces the effort required by the compiler to perform global optimizations and searches across the full RTL hierarchy. For complex SoCs, this can significantly reduce compilation time.

🔍 Role of PDUSpec

PDUSpec complements PDU by controlling signal visibility during simulation. In large SoCs, the simulator processes a vast number of signals and hierarchical paths, which can slow down simulation and generate unnecessary debug data.

By specifying PDUSpec, only the relevant signals and modules are visible to the simulator, reducing simulation overhead and improving performance. This targeted visibility not only speeds up simulation but also helps engineers focus on functional coverage, corner-case scenarios, and assertion-based verification without being distracted by irrelevant signal activity.

🚀 Benefits of Using PDU and PDUSpec

- Reduced compilation and simulation times

- Efficient management of large and complex SoC hierarchies

- Improved performance through targeted signal visibility

- Faster regression cycles and enhanced verification productivity

🧠 Conclusion

Together, PDU and PDUSpec enable a scalable, efficient, and manageable verification flow. Compilation and simulation times are dramatically reduced, regression cycles become faster, and engineers can focus on ensuring design correctness rather than waiting on builds. For large SoC projects, mastering these Questa® features is critical to achieving fast, reliable, and maintainable verification workflows.

A well-articulated and informative post! Kudos to the engineering team for simplifying a complex topic and demonstrating our organization’s technical depth. Proud to see such thought leadership emerging from within our team.